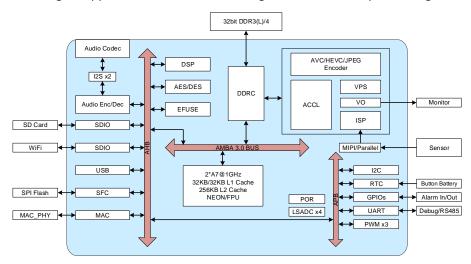

XS7310 is a high-performance digital SoC designed specifically for smart IPC (IP Camera) applications. It features advanced ISP technology and state-of-the-art H.265 (HEVC), H.264, and JPEG encoders. The chip integrates DDR3/3L/4 memory (1866 Mbps), USB 2.0, POR, RTC, and audio codec. It also supports a wide range of interfaces, including MIPI, I2C, SPI, GPIO, and UART, and provides output for commonly used peripheral clocks. XS7310 supports high-definition CMOS sensor input, which is processed by the ISP, followed by video preprocessing and compression via the audio/video encoder, enabling triple stream output. Equipped with a built-in CPU, GPU (supporting OpenVX/OpenCL), and a CNN hardware acceleration unit, the chip can handle mainstream intelligent applications such as facial recognition and license plate recognition.

#### Processor

- Dual-core ARM Cortex-A7@1GHz, 32KB I-Cache, 32KB

D-Cache, 256KB L2 Cache

- Integrated FPU. Supports NEON acceleration.

# Video Encoding

- Real-time multi-stream H.265/H.264 encoding capability: Up to (4M + 720P + D1)@30 fps

- Supports CBR/VBR bitrate control

- Supports ROI encoding

- Supports smart encoding

### JPEG Encoding

Supports JPEG Baseline encoding: Snapping up to 4M@10 fps

### Audio Encoding

- Supports audio codec of G711 A/U, G726, and AAC

- Supports AEC for voice intercom

## Intelligent Analysis

- Supports deep learning CNN acceleration and standard

CAFFE and Tensorflow network models

- 192 INT16 MAC addresses and 768 INT8 MAC addresses

- Supports computing capability up to 1TOPS

## Video and Image Processing

- Supports frame rate control of 1 to 60 fps

- Supports image cropping and scaling from 1/16x to 16x

#### ISP

- Supports static & dynamic bad pixel correction and black level correction

- Supports raw domain 2D de-noising and YUV domain 2D/3D de-noising

- Supports digital gain control, lens shading correction, and strong light suppression

- Supports 3A (AE, AWB, and AF)

- Supports 2F-1 HDR and LWDR

- Supports GIC, color correction, and GAMMA correction

- Supports edge enhancement, defogging, and digital light supplement

### Video Interface

- Supports 1 × 4 or 2 × 2 lane MIPI and parallel interface input

- Supports BT.1120 input and output

- Supports 1-ch 16/18/24-bit RGB parallel LCD output

- Supports MIPI DSI TX output

- Supports 1-ch CVBS video output (PAL and NTSC formats)

## Audio Interface

- Built-in audio codec. Supports up to 24-bit, 96kHz sampling

- Supports I2S interface for external audio codec

- Supports privacy masking for up to 8 independent regions

- Supports OSD and BMP graphic overlay

- Supports image rotation and flipping (mirroring)

- Supports LDC (Lens Distortion Correction)

# Network Interface

Ethernet MAC interface supports RMII mode and full-duplex/half-duplex operation of 10/100 Mbps

# Packaging

14.3 mm × 14.3 mm, 396 pins, pin-to-pin distance of 0.65 mm, TFBGA